|

一博高速先生成员--黄刚 咋滴,不知道“ILD”就做不好高速设计啦?感觉是为大家做不好高速信号又找到了一个新的借口是吧。言归正传,对于很多硬件的朋友或者设计的朋友,说起高速信号的无源指标,第一反应就是插损。插损是SI的专业术语,用很多朋友自己的话来说就是损耗或者叫衰减。当然这个指标也是很重要,通常去设计一个长链路的时候,协议的插损要求影响着布线的长度,板材的选择,芯片间的布局甚至的结构的变更等,所以我们经常遇到很多客户都关心损耗能不能满足要求,满足的情况下能不能尽量小。

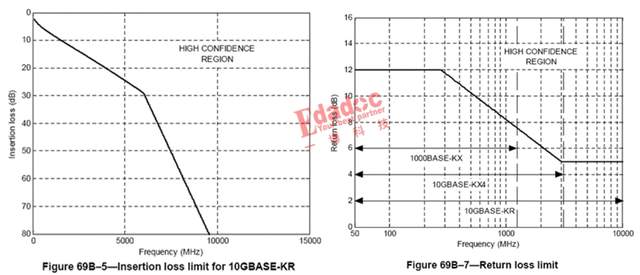

我们就以大家比较熟悉的10GBase-KR信号为例,来介绍今天的猪脚“ILD”。先请出大家比较熟的插损和回损的协议要求,10Gbps信号,我们在插损指标上关心的是5GHz位置的损耗情况,为什么10Gbps信号看的是5GHz频点呢?这个可以翻翻刚写不久的这篇文章《明明我说的是25G信号,你却让我看12.5G的损耗?》,看完相信就不会再有疑问了。另外顺便提下回损,回损在协议中一般会覆盖到基频的2倍,10GBase-KR插损回损的协议指标就如下所示了。

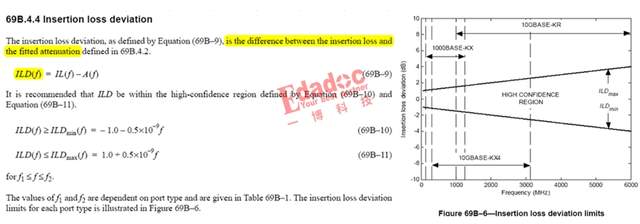

当然,对于大家都比较熟悉的东西,高速先生通常就一笔带过了。当然,上面的插损回损这些无源指标都出自于IEEE的文档中,不得不说,文档的页数是真的不少,所以我们有理由相信大家在找到插损回损指标后就关闭它了。如果稍微有一点点恒心的话,其实这个10Gbps信号还有一个很重要的指标,就是“ILD”了,指标是这样描述的:

ILD指标,翻译成中文可以叫做插损偏离度。高速先生帮大家理解下哈,其实它讲的是在我们仿真得到某条高速设计链路的插损后,然后协议的算法会去做真实插损曲线的fitted曲线,所谓fitted曲线,其实就是算法根据实际得到的插损曲线通过几个基本算法取平均值,得到的就是理想插损情况和真实插损情况的关系式。然后通过ILD指标来表征他们之间的差距,协议要求这个差距必须在一个范围内,不能太大。

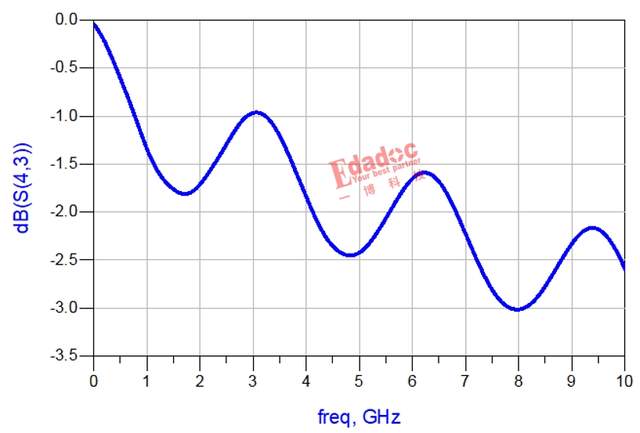

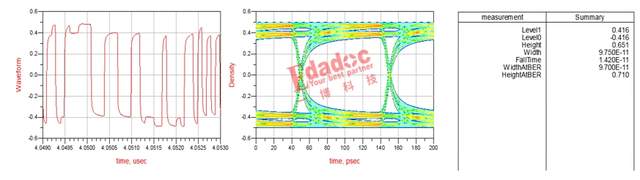

没关系,大家也知道高速先生的作风,一定会让大家弄懂。我们来举个例子哈,假设我们提取到某个实际设计链路的插损曲线是下面这样的,是不是有一些自己做仿真的朋友也曾经提取过这样的参数呢?当然大家第一反应就觉得不是很好是吧,但是如果从插损的协议指标来看,却又是很轻松能满足协议要求的。

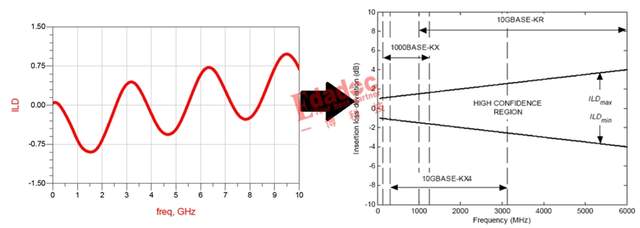

那么这个时候可以用ILD指标去卡,通过协议的算法就得到了上面这个真实链路的fitted曲线,就是下面红色这条。

然后根据ILD的公式,用真实的插损曲线(蓝色)减去fitted出来的理想插损曲线(红色),就得到了ILD的结果:当然你就可以和上面的ILD协议要求去对照了。还好,看起来也还在ILD协议要求范围内。

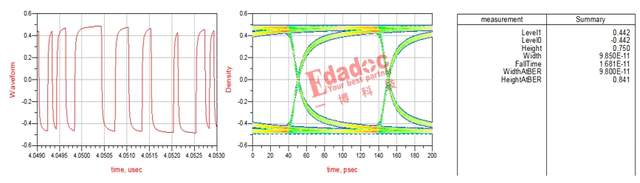

那到底这个ILD的指标对信号质量有多少的影响度呢?我们通过大家都觉得比较直观的眼图来介绍哈。 我们首先就比较真实的插损和fitted后的插损对眼图的影响,用两个插损S参数模型分别在10Gbps数据通道去跑眼图,峰峰值为1V的发送信号。我们首先看看fitted插损的眼图结果:还不错,眼图有841mV,眼宽是98ps。

那么我们再看看真实插损参数的眼图结果,大家猜猜是变好还是变差呢?

那必须是变差啊!都说了fitted走线是真实插损的理想情况了,眼图结果如下:眼高居然只有710mV了,眼宽也减小了,只有97ps。

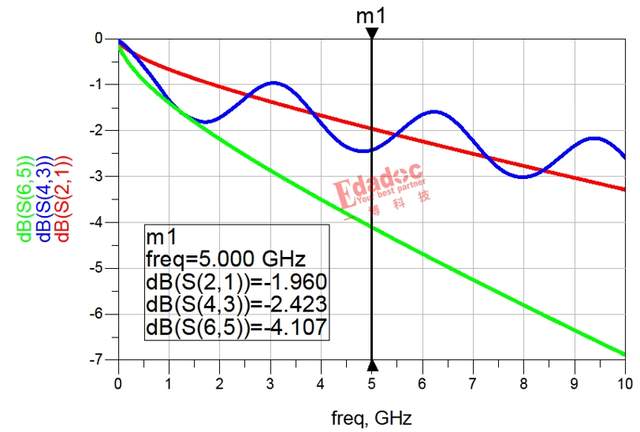

可恶!原来我们仿真出来的插损曲线和理想情况下的居然还真不小。可见这个ILD指标还是有它本身的意义在里面。为了再证明下ILD指标的重要性,我们再加一种插损的case去仿真。按照上面说的,fitted曲线是真实插损的理想版,好是正常的。那么我们就加一种case,就是下面绿色的插损case。

红色的fitted曲线比专业术语真实的蓝色插损曲线的眼图结果好了很好,那么有没有可能并不是红色的曲线好,而是蓝色的真实链路插损差呢?那么我们就加了绿色的这条曲线,绿色曲线在所有频段都比蓝色的真实插损要差,尤其是高频部分,多出一倍的损耗。如果像以前只按照插损的协议指标去卡的话,绿色肯定比蓝色要差很多很多。大家觉得用绿色的插损曲线去跑眼图,结果会真的差很多很多吗?

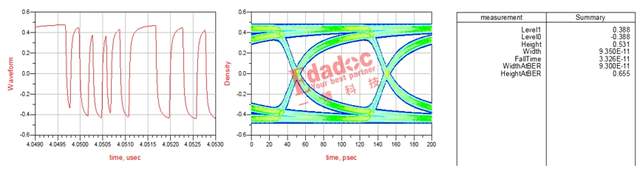

结果是下面这样的:眼高655mV,眼宽93ps。

真出乎意料啊!肉眼可见大了一倍损耗的绿色曲线,居然并没比真实的蓝色插损曲线的眼图结果差太多,这的确也再一次证明ILD这个指标存在的意义,单单看插损指标并不能很好的保证链路的信号质量。最后总结一下,从插损的结果来看,现在大家知道了的插损曲线在不同频率之间的波动如果很大,那必然它的ILD指标就不会很好,同时也会非常影响眼图的性能。那么回归到设计上,到底会有哪些设计问题导致ILD指标比较差呢?没错,大家又猜对了,这个就是高速先生留给大家的问题了哦! 问题:到底在高速信号PCB设计中,哪些设计问题可能会导致插损的ILD指标变差呢?

版权声明

“特别声明:以上作品内容(包括在内的视频、图片或音频)为用户上传并发布,本平台仅提供信息存储空间服务。

Notice: The content above (including the videos, pictures and audios if any) is uploaded and posted by the user , the platform merely provides information storage space services.”

本文地址: https://amtbbs.org/thread-17657-1-1.html

|  |联系我们|法律声明|用户协议|AMT咨询|商务合作|会员入驻|积分充值|积分商城|积分奖励规则|TradEx全球购|加入QQ技术群|添加企业微信|加入微信技术群|文章投稿|手机版|小黑屋|

世界先进制造技术论坛™(简称AMT™, 制造知网™)

( 沪ICP备12020441号-3 )

|联系我们|法律声明|用户协议|AMT咨询|商务合作|会员入驻|积分充值|积分商城|积分奖励规则|TradEx全球购|加入QQ技术群|添加企业微信|加入微信技术群|文章投稿|手机版|小黑屋|

世界先进制造技术论坛™(简称AMT™, 制造知网™)

( 沪ICP备12020441号-3 )